Physical Verification Introduction

After routing, your layout is complete. Now a number of checks are performed to verify that the drawn layout works as intended.

- Physical verification

- Equivalence Checking

- Timing Analysis

Equivalence check will compare the netlist we started out with (pre-layout/synthesis netlist) to the netlist written out by the tool after PnR(postlayout netlist).Physical verification will verify that the post-layout netlist and the layout are equivalent. i.e. all connections specified in the netlist is present in the layout.This article explains physical verification.

Physical Verification

After routing, your PnR tool should give you zero DRC/LVS violations. However, the PnR tool deals with abstracts like FRAM or LEF views. We use dedicated physical verification tools for signoff LVS and DRC checks. Some of these are Hercules from Synopsys, Assura from Cadence and Calibre from MentorGraphics.

The major checks are:

- DRC

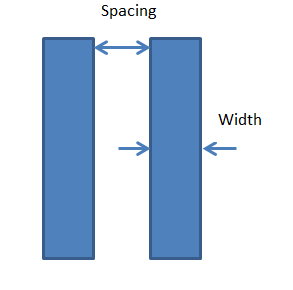

DRC checks determine if the layout satisfies a set of rules required for manufacturing. The most common of these are spacing rules between metals, minimum width rules, via rules etc.There will also be specific rules pertaining to your technology. An input to the design rule tool is a ‘design rule file’ (called a runset by Synopsys’ hercules). The design rules ensure sufficient margins to correctly define the geometries without any connectivity issues due to proximity in the semiconductor manufacturing processes, so as to ensure that most of the parts work correctly. The minumum width rules exists for all mask layers, and spacing between the same layers are also specified. Spacing rules may change depending on the width of one or both of the layers as well. There can also be rules between two different layers, and specific via density rules etc. If the design rules are violated, the chip may not be functional.DRC checking software, like Assura, Hercules or Calibre usually takes the layout in any of the supported formats, like GDSII. - LVSLVS is another major check in the physical verification stage. Here you are verifying that the layout you have created is functionally the same as the schematic/netlist of the design-that you have correctly transferred into geometries your intent while creating the design. So all the connections should be proper and there shouldn’t any missing connections etc.The LVS tool creates a layout netlist, by extracting the geometries. This layout netlist is compared with the schematic netlist. The tool may require some steps to create either of these netlists(e.g. nettran run in synopsys)

If the two netlists match, we get an LVS clean result. Else the tool reports the mismatch and the component and location of the mismatch. Along with formal verification, which verifies if your pre-layout netlist matches the post-layout netlist,LVS verifies the correctness of the layout w.r.t intended functionality.Some of the LVS errors are:- Shorts – Wires that should not be connected are overlapping.

- Opens – Connections are not complete for certain nets.

- Parameter mismatch – LVS also checks for parameter mismatches. e.g. It may match a resistor in both layout and schematic, but the resistor values may be different. This will be reported as a parameter mismatch.

- Unbound pins – If the pins don’t have a geometry, but all the connection to the net are made, and unbound pin is reported.

- Antenna

- ERC

ERC (Electrical rule check) involves checking a design for all electrical connections that are considered dangerous. - Floating gate error – If any gate is unconnected, this could lead to leakage issues.

- VDD/VSS errors – The well geometries need to be connected to power/Ground and if the PG connection is not complete or if the pins are not defined, the whole layout can report errors like “NWELL not connected to VDD.

Process antenna effect or “plasma induced gate oxide damage” is a manufacturing effect. i.e. this is a type of failure that can occur solely at the manufacturing stage. This is a gate damage that can occur due to charge accumulation on metals and discharge to a gate through gate oxide.

Let us see how this happens. In the manufacturing process, metals are built layer by layer. i.e. metal1 is deposited first, then all unwanted portions are etched away, with plasma etching. The metal geometries when they are exposed to plasma can collect charge from it. Once metal1 is completed, via1 is built, then metal2 and so on. So with each passing stage, the metal geometries can build up static electricity. The larger the metal area that is exposed to the plasma, the more charge they can collect. If the charge collected is large enough to cause current to flow to the gate, this can cause damage to the gate oxide. This happens because since the layers are built one-by-one, a source/drain implant may not be available for discharge as in fig.b.

Antenna rules are normally expressed as an allowable ratio of metal area to gate area. Each foundry sets a maximum allowable antenna ratio for its processes. If the metal area–which is cumulative, i.e. the sum of the ratios of all lower layer interconnects in addition to the layer in check–is greater than the allowable area, the physical verification tool flags an error.For example, let’s say maximum allowable antenna ratio for metal1 is 400. If the gate area is 1 sq.u and if the metal area connecting to the gate is 500 sq.u, there will be a process antenna violation.

You may be also interested in below topics

I am a Recruiter Looking for someone in Physical Design and Verification. if someone can help me with this.

ReplyDeleteVerification Engineer :

• Expertise with AXI/AHB/APB protocols

• Knowledge/Expertise with PCIe/MIPI will be an added advantage

• Knowledge with processor verification is a plus

• Extensive knowledge of SystemVerilog and verification methodologies particularly OVM/UVM

• Strong experience in the implementation of verification infrastructures, test benches, models, assertions

• Expertise with development of constrained random tests scenarios

• Running regression tests and analysis of results including functional coverage

• Hands on with RTL/Gate Level Simulation

• Expertise with industry standard tools like VCS/Verdi/NCSim/Questa etc.

• Scripting skills with PERL/TCL

• With Excellent communication and interpersonal skills

• Very good team player, self motivated and creative in problem solving

Physical Design :

Education Background with VLSI skills ( Engineering Degree in Electronics & Communication or Electrical )

* Hands on working exposure to Synthesis and/or Custom/Partition/Block level Physical design .

* Exposure to Design Compiler, IC Compiler , Z Route, Timing using PT/PTSI, Physical verification DRC,LVS

* Should have gone through one or more tape outs in 10nm or 14nm and beyond

Knowledge on the below areas is required

Synopsys Tools (ICC , DC, PT)

PnR and Physical Verification

Floorplanning

Std cell placement.

Timing driven methodologies for better QoR

CTS

Routing and optimizations.

Maxcap / Maxtrans Fixes..

Partition Level Timing Debugging and fixing using PTSI

SPEF extraction

LVS, DRC, ANT & Density problems

Scripting (TCL)

Contact- 8249483253

Email Id- somnath@bharatheadhunters.com

Linkedin- https://www.linkedin.com/in/golati-somnath-achary-0a5309127

nice

ReplyDeleteCommercial video production companies

ReplyDeleteA commercial video production is a short-form video that briefly describes your product, service or brand promise. Their intent is to build up brand loyalty and inspire a call to action. Typically, commercials: Seek to establish an emotional connection with your audience. Feature professional onscreen and voice talent.

Parks and recreation software

ReplyDeleteThe recreation software streamlines the management of your operations, which reduces back-office tasks, increases efficiency, and boosts revenue all in one place. The software programs are made up of comprehensive modules equipped with a wide variety of features to cover any and every recreational need.